reference : AN-408 (MV-S302820-00) PTP System Design Considerations

-

Instruction

-

PTP 시스템 디자인시에는 몇가지 고려할 사항이있는데 특히 아래 두가지 경우와 같이 복합 시스템 구성시에 중요하다

-

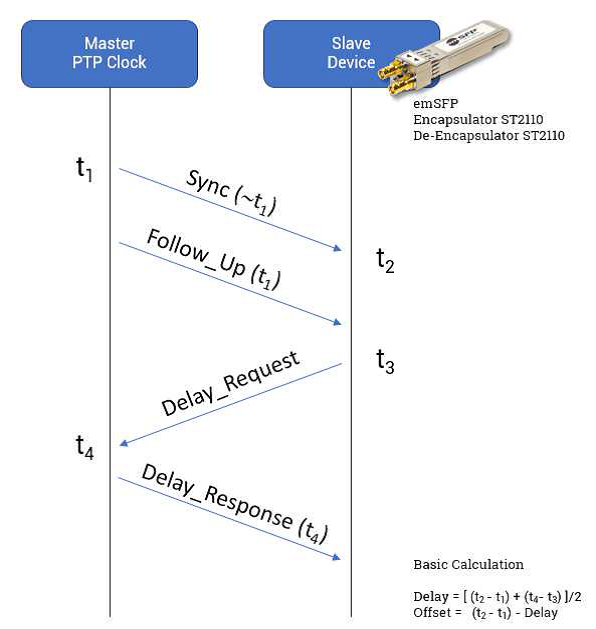

PTP 는 UDP 패킷을 이용하여 Master Clock 에 동기화 하는 개념이다

-

크게 아래의 4단계로 나누어진다

-

아래 두가지 경우에 어떻게 다르게 동작하는지 체크해 보겠다.

-

첫번째는 스위치와 PHY 로 구성된 시스템이 TC (Transparent Clock) 으로 동작할때

-

둘째는 두개이상의 스위치가 상호 연결되어 BC (Boundary Clock) 으로 동작할때

-

시스템 요구 사항

-

시스템에 PTP 를 구현하려고 할때 고려할 사항은

-

포트중에 어떤 포트가 지원을 해야하는지

-

어느정도의 정확도를 필요로 하는지 : 예를 들면 스위치내부 FIFO 로 인한 지연은 정확한 고정시간이없다, 또한 정확도를 높이는 방법으로는 타임스템프를 시트템의 맨 바깥 (ex. PHY) 에서 처리하도록 하는게 좋다

-

Implementation Requirement

-

Clock Oscillator

-

BC 에서만 오실레이터가 필요하고 TC 나 SyncE 에서는 외부의 오실레이터가 따로 필요없다.

-

즉, PTP_REF_CLK 의 입력으로 오실레이터를 쓰느냐 내부에서 만든 SyncE 클럭이나 main 25MHz ref_clk 에 따라서 지원하는 범위가 다르게 된다.

-

Initial Phase Synchronization

-

두개이상의 디바이스로 구성된 한개의 시스템에서 TOD 동기화를 위해서 External Pulse Pin 을 사용한다

-

마스터디바이스는 Pulse 출력을 해주고, Slave 들은 입력을 받는데 각각의 Slave 는 Master 로부터의 Trace 길이가 다르므로 Propagation Delay 를 가지게 된다. 그러므로 이것을 보상해 주어야한다.

-

Periodic Phase/Frequency Synchronization

-

Multi-Device 시스템에서는 TOD 불일치 가능성이 있으므로 주기적으로 업데이트가 필요하다

-

최적의 방법은 모든디바이스를 같은 클럭소스를 받게하고 PPS 핀을 연결하는것이다.

-

Pulse and PPC Test Points

-

Pulse Delay 측정 을 위해서는 Load Time (PPS Output 신호가 나오기까지 시간) 을 측정한다

-

입력은 PTP_CLK(Master는 출력, Slave 는 입력), 출력은 PTP_CLK_OUT 핀

-

Multi-Device System Example

-

Multi-Device System Exaple

-

-

Multi-Device System with FPGA

-